| LPDDR4 与 DDR4 与 LPDDR4x 内存:有何不同? | 您所在的位置:网站首页 › ddr4 3200与2666区别 › LPDDR4 与 DDR4 与 LPDDR4x 内存:有何不同? |

LPDDR4 与 DDR4 与 LPDDR4x 内存:有何不同?

|

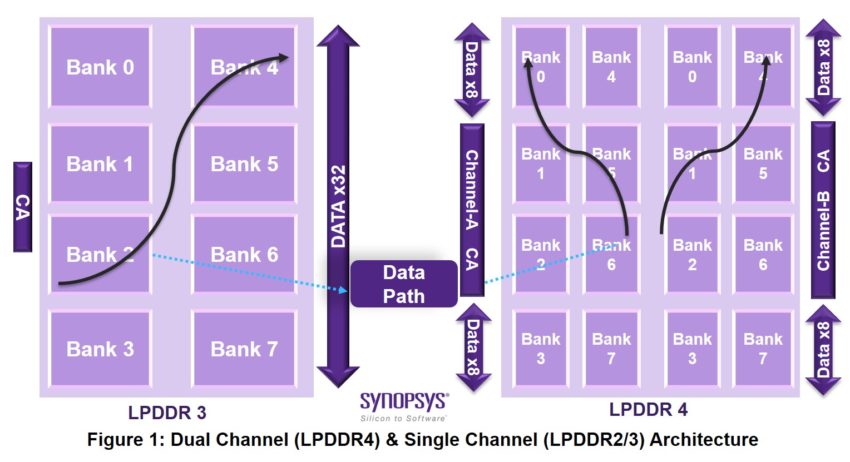

LPDDR4 相当于移动设备上的 DDR4 内存,与 DDR4 相比,它具有更低的功耗,但是以带宽为代价的。LPDDR4 具有双 16 位通道,因此每个 DIMM 有 32 位总线。相比之下,DDR4 每个 DIMM 具有 64 位通道。但是,与此同时,LPDDR4 具有更宽的 16n 预取,每个通道总共(16 words x 16 bit)256 bit/32 bytes,是两个通道组合的两倍。

另一方面,DDR4 的每个通道有两个 8n 预取,可将数据传入和传出控制器。两个 bank 是独立的,可以执行两个独立的 8n 预取,这是通过使用多路复用器对其内部组进行时分多路复用来完成的,每个组每个周期总共有 8 words x 64 bit = 512 bits(64 bytes)。

与 DDR4 相比,LPDDR4 功耗更低,但以带宽为代价。LPDDR4 具有双 16 位通道,导致总总线为 32 位。相比之下,DDR4 具有 64 位通道。 LPDDR4 还具有更灵活的突发长度,范围从 16 到 32(256 或 512 bits,32 或 64 bytes),主要使用 16 BL。另一方面,DDR4 限制为每个周期 8 个突发长度(128 bits或 16 bytes),每个 bank 可以执行额外的传输(来自两个不同的 bank 组)。

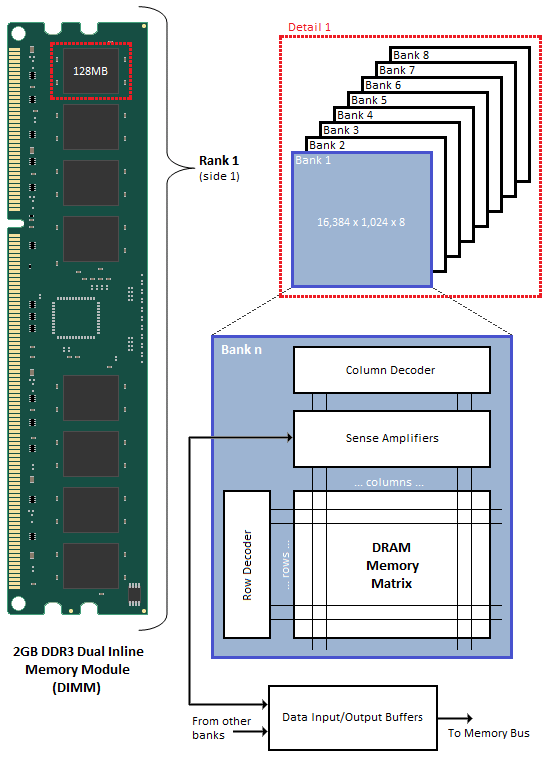

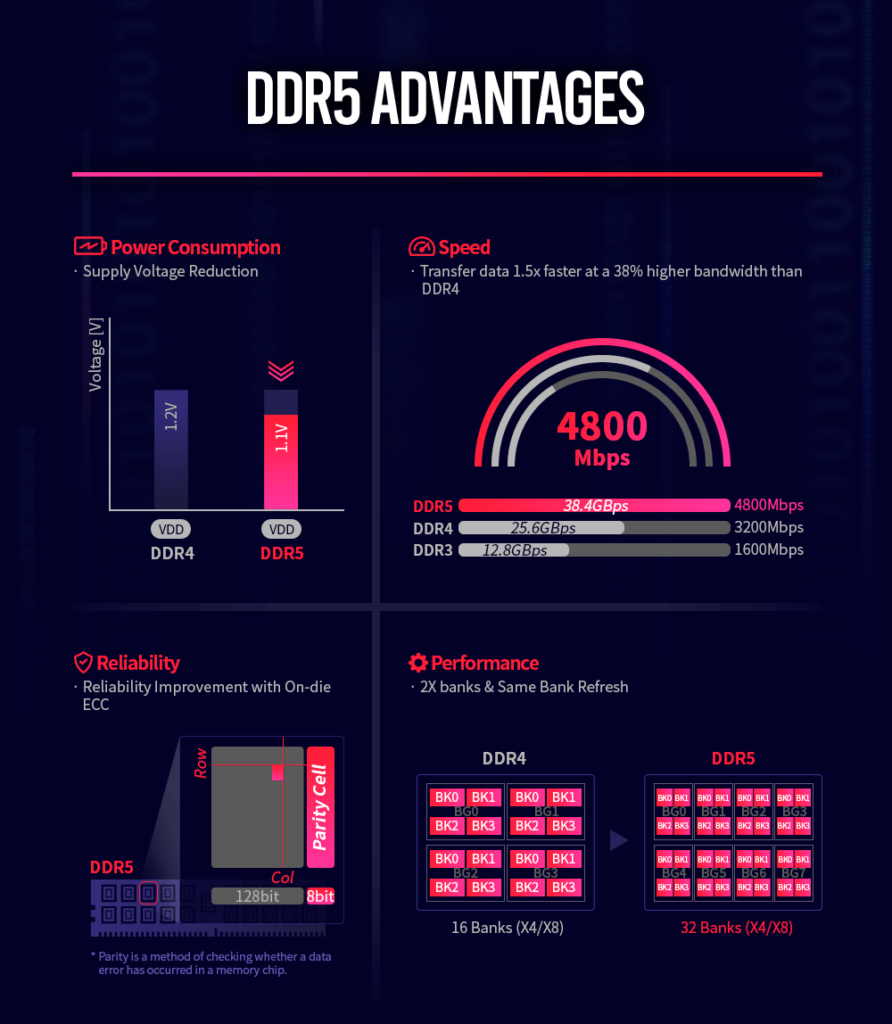

要了解突发长度的含义,需要知道内存是如何访问的。当 CPU 或缓存请求新数据时,将地址发送到内存模块和所需行,然后定位该列(如果不存在,则加载新行)。请记住,每一步之后都会有延迟。 之后,整个列以突发方式通过内存总线发送。对于 DDR4,每次突发为 8(或 16B)。对于DDR5,它已经增加到 32 (最高 64B)。每个时钟有两个突发,它们以有效数据速率发生。此外,与 LPDDR4 类似,DDR5 每个 DIMM 有两个 32 位通道,在双 DIMM 配置中总共有四个通道,预取和 BL 也增加到 16。这个数字其实是理想的,因为内存中的每个高速缓存线都具有相同的大小。 与标准 DDR4 内存相比,这种设计使 LPDDR4 的能效更高,非常适合用于电池待机时间长达 8-10 小时的智能手机。美光的 LPDDR4 RAM 以 2133 MHz 时钟频率,传输速率为 4266 MT/s,而三星紧随其后,时钟频率为 1600MHz,传输速率为 3200 MT/s。此外,正如在下表(来自维基百科)中所见,LPDDR4 (1.1v) 的电压比 DDR4 (1.2v) 低得多,尽管具有相似或更高的 I/O 总线时钟。

DDR

低功耗DDR 摩托罗拉新旗舰采用美光制造的 LPDDR5 RAM

来源 最后,还有内存Bank的问题,LPDDR4 再次针对低功耗进行了优化,而 DDR4 内存则相反。虽然 DDR4 内存由 16 个Bank组成,每个Bank Group包含四个独立的Bank,但 LPDDR4 和 LPDD4X DIMM 每个通道共有八个Bank,因此总数量为 16 个(16-bit x 2)。LPDDR5采用了类似于DDR4的结构。

与 DDR5 降低电压和功耗的方式类似,LPDDR4X 也是如此,它将 I/O 电压降低了 50%(1.12 至 0.61v),大大降低了内存和内存控制器的功耗。 此外,速度也从3200MT/s提升到4266MT/s(无OC),这是使用更快的 I/O 总线时钟(1600MHz 至 2134MHz)和内存阵列(200-266.7MHz)的结果,命令和地址总线保留了 6 位 SDR 空间。最后,它占用的片上空间更小,单个封装最多可包含 12GB 的 DRAM。不利的一面是,LPDDR4X 不向后兼容 LPDDR4,即使设备与更快的 LPDDR4 内存兼容,它也可能无法与 LPDDR4X 一起使用。 LPDDR4/LPDDR4x 与 LPDDR5 与 DDR5LPDDR5 比 LPDDR4 和 LPDDR4x 更节能。由于使用了动态电压缩放 (DVS),它可以根据负载调整电压,进而调整内存频率。与LPDDR4/4x一样,LPDDR5 也具有双 16 位通道,以及高达 32(主要是 16)的突发长度。 另一方面,DDR5 每个 DIMM 具有两个 32 位通道(DDR4 每个通道有一个 64 位),每个通道的突发长度和预取为 16n(DDR4 只有一半)。根据 JEDEC 标准,DDR5 和 LPDDR5 都将支持高达 6400 Mbps 的速度,尽管我们不会在第一波模组中看到它们。LPDDR5 还将密度提高到每通道 32Gb,工作电压低至 VDD 1.05/0.9V 和 I/O 0.5/0.35V。 LPDDR5 DRAMLPDDR4 DRAM设备尺寸2Gb 到 32Gb(每通道) 4、8 和 16 个 bank 设备 1k、2k 和 4k 页面大小2Gb 至 16Gb(每通道) 8 个 bank 设备 2k 页大小速度高达 6400 Mbps高达 4266 Mbps电压1.8V DRAM 阵列 1.05V / 0.9V 核心 0.5V / 0.3 VI/O1.8V DRAM 阵列 1.1V 核心 1.1V / 0.6VI/O由于使用了动态电压缩放 (DVS),LPDDR5 可以支持两种电压模式:1.05V (C) 和 0.5V (I/O),高频时 0.9V (C) 和在低率下工作时0.3V (I/O) 。 LPDDR5 功能包括用于命令/地址 (C/A) 时钟 (CK) 的全新可扩展时钟架构,以实现更轻松的 SoC 时序收敛,以及 DDR5 的大部分功能,例如决策反馈均衡器 (DFE)、Write X 功能以节省功耗,并链接 ECC 以增强内存通道 RAS。 最后,LPDDR5 还具有更灵活的 bank 结构。虽然 DDR5 包含 32 个Bank,但它的移动版本可以从 4 到 16 个Bank不等,最多有四个Bank组(尽管 1-2 是标准)。总体而言,LPDDR5 提高了电源效率,以及移动内存的频率和带宽,同时保留了 LPDDR4/LPDDR4x 众所周知的灵活性。 |

【本文地址】